AVR은 8-비트 RISC(Reduced Instruction Set Computer) 구조로 명령어가 간단하며 동작 속도가 빠르고, 1MHz당 약1MIPS(Million Instruction Per Second)의 성능을 보인다. AVR의 대표적인 특징은 다음과 같다.

● 향상된 RISC 구조

- 133개의 강력한 명령어들이 대부분 단일 클럭으로 실행된다

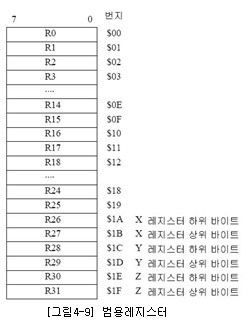

- 32 X 8 범용 동작 레지스터 + 주변 콘트롤 레지스터로 구성

- 16MHz 환경에서 16 MIPS 이상의 성능

- 2 사이클 곱셈기를 칩에 내장

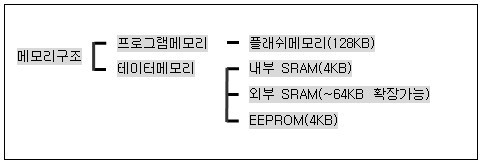

● 프로그램과 데이터 메모리

- 128K Byte In-System 프로그램 플래쉬 메모리 (내구성 : 최대 10,000번 쓰고 지울 수 있다.)

- 칩에 내장된 부트 프로그램으로 In-System 프로그래밍 가능

- 4K Byte EEPROM (내구성 : 최대 100,000번 쓰고 지울 수 있다.)

- 4K Byte 내장형 SRAM

- 최대 64K Byte 이상의 외부 메모리 영역을 갖는다.

● JTAG (IEEE std. 1149.1 호환) 인터페이스 제공

- JTAG 인터페이스로 플래쉬, EEPROM, 퓨즈와 락비트를 프로그래밍 가능하다.

● 주변 사양

- 프로그래밍 가능한 53개의 Input / Output

- 외부 인터럽트 Ext. INT 8개

- 두 개의 8-bit Timer/Counters / 두 개의 16-bit Timer/Counters

- 두 개의 8-bit PWM 채널 / 6개의 16-bit PWM 채널과

- 8 채널, 10bit ADC

- 두 개의 프로그램 가능한 직렬 USART 제공

- 마스터 / 슬레이브 SPI 직렬 인터페이스

- 칩 내장형 아날로그 비교기

● 독특한 마이크로콘트롤러 사양

- 파워온 리셋 과 프로그램가능한 Brown-out 감지기

- 6가지 슬립모드 : 아이들, ADC 노이즈 감쇄기, 저전원, 무전원, 대기상태, 연장 대기상태

- 모든 Pull-up 설정해제

● I/O 와 패키지

- 53개의 프로그램 가능한 I/O 라인 , 64개의 TQFP와 64패드 MLF

● 동작 전원

- ATmega128L : 2.7V ~ 5.5V - ATmega128 : 4.5V ~ 5.5V

● 동작 속도

- ATmega128L : 0 ~ 8MHz - ATmega128 : 0 ~ 16MHz

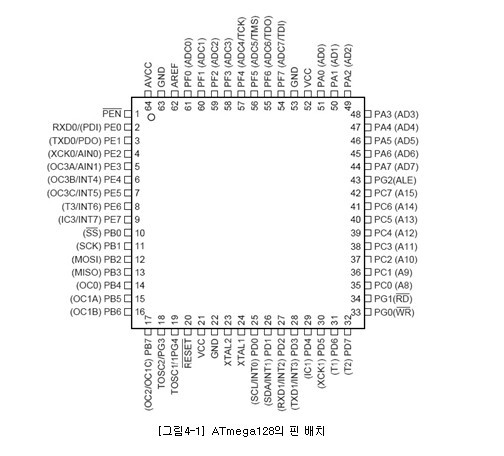

04. AVR128의 외부구조

• VCC(21,52) | 마이크로프로세서가 동작하도록 공급하는 전원으로 두 가지 타입에 따라 전원의 범위가 다르다. ( ATmega128L : 2.7V ~ 5.5V / ATmega128 : 4.5V ~ 5.5V ) | |

• GND(22,53,63) | 신호의 접지 핀으로 사용된다. | |

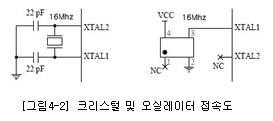

• XTAL1, XTAL2(23,24) |

| |

• RESET(20) | 리셋 입력 핀으로서 50ns 이상의 Low level 입력이 지속되면 리셋이 발생한다. | |

• PORT A/B/C/D/E | 반이중 I/O 포트로 내부 풀업 저항된 8비트/양방향/병렬/범용 포트이다. DDRX, PORTX, PINX 의 레지스터를 이용해 제어를 한다. | |

• PORT F | 반이중 I/O 포트로 내부 풀업 저항된 8비트/양방향/병렬/범용 포트이다. A/D컨버터의 입력포트로도 사용된다. | |

• PORT G | 반이중 I/O 포트로 내부 풀업 저항된 5비트/양방향/병렬/범용 포트이다. | |

• AVCC(64) | A/D 컨버터 및 포트 F의 전원 (ADC를 이용하지 않더라도 외부적으로 VCC에 연결되어야 한다.) | |

• AGND(63) | AVCC에 대한 전원 접지(반드시 GND와 접속할 것) | |

• AREF(62) | A/D 컨버터의 기준전압 | |

• PEN(1) | SPI 활성화를 시키는 프로그래밍 인에이블 핀으로서 파워 온 리셋 시 LOW로 유지함으로써 SPI 활성화 상태가 된다. 일반적인 동작모드에서는 사용하지 않는다. |

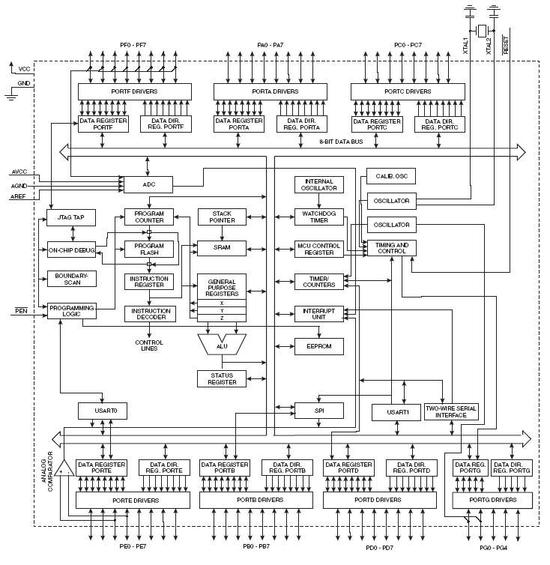

05. AVR128의 내부구조

ATmega128의 내부구조는 아래 [그림4-3] 블록도와 같다.

- 프로그램 / 데이터에 대해 분리된 메모리와 버스가 사용된다.

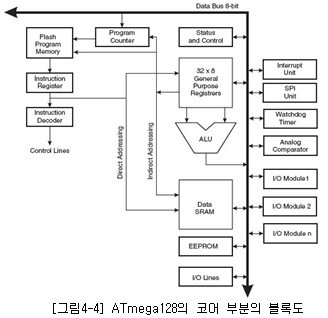

● 고성능의 ALU는 모든 32개의 범용레지스터와 직접 연결되어 단일 사이클로 동작한다.

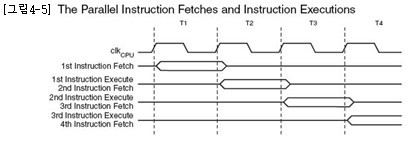

● ATmega128이 하버드구조와 2단계 파이프라인 처리방식으로 프로그램 명령을 인출하여

실행하는 동작을 [그림4-5] 에 보였다. AVR의 이러한 진보된 설계 기술은 결국 CPU가 시스템

클럭의 1주기에 평균적으로 1개의 명령을 실행하도록 함으로써 클럭 주파수 1MHz당 1MIPS의

처리속도에 해당하는 매우 높은 성능을 발휘하는 것이 가능하도록 하였다.

● [그림4-6]과 같이 1클럭 사이클 동안에 1개의 명령에서 2개의 레지스터 오퍼랜드가 사용되는 연산을 수행하고 그 결과를 다시destination register에 저장하는 처리한다.

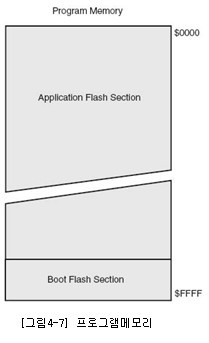

(1) 프로그램메모리

ATmega128은 내부에 프로그램 메모리로 사용하는 128KB의 플래쉬 메모리를 가지고 있다.

① Flash Memory

- 128Kbyte (64K * 16bit)

- 16bit or 32bit

- Application / Boot Flash section

- Programming Writing

• SPI 통신방식을 이용한 ISP기능 이용

• JTAG 에뮬레이터 사용

• 병렬 프로그래밍 모드 이용

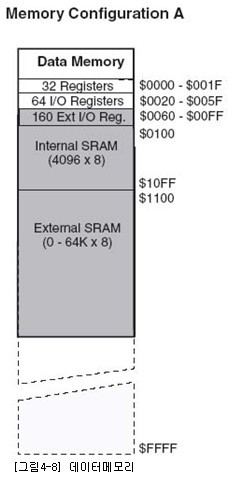

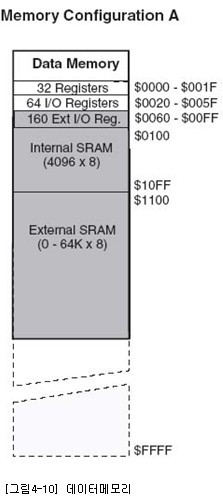

(2) 데이터메모리

ATmega128의 테이터메모리는 내부 데이터 메모리로서의 SRAM, 외부 데이터 메모리 SRAM, 그리고 내부 EEPROM로 3가지 종류로 나눌 수 있다.

① 32 Registers ($00~$1F)

- 32레지스터는 AVR 모든 시리즈에서의 사용되는

범용레지스터로서의 역할을 하게 된다.

② 64 I/O Registers ($20~$5F)

- 각종 I/O 디바이스들을 제어하기 위한 레지스터

- IN / OUP 명령 사용 ($20~$5F → $00~$3F 라고 지정해야 한다.)

- ATmega128 datasheet (p.355~p357참조)

③ 160 Ext I/O Registers ($60~$FF)

- ATmega128에 추가된 각종 I/O 디바이스들을 제어하기 위한 레지스터

- IN / OUP 명령어 대신 LD/LDS/LDP, ST/STS/STD 명령어를 사용해야 한다.(∵16bit)

- ATmega128 datasheet (p.355~p357참조)

④내부 SRAM (0x0100~0x10FF)

- 4Kbyte (4096 * 8bit)

- 각종 사용자변수 / 스택 영역으로 사용

- 사용자가 정해진 4KB보다 더 확장된 데이터메모리를 필요할 때 약 60KB의 외부 데이터 메모리영역으로 이용 가능하다.

- 4Kbyte 내장

- 불 휘발성

- 다른 데이터 메모리 어드레스 영역과는 별

개의 영역을 할당 받게 된다.

- 단일 바이트로 읽고 쓸 수 있다.

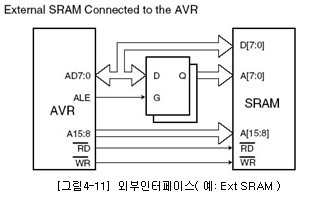

07. AVR128의 외부인터페이스

외부 메모리 인터페이스가 제공되며 외부 SRAM / 플래쉬 / LCD 디스플레이 / ADC 와 같은 외부 메모리 장치에 대한 인터페이스를 구동시키는데 아주 적합하게 되어 있다.

[출처] AVR 세미나 : ATmega128 2차 / AVR128 구조|작성자 표윤석